Exploring Look Up Tables in FPGAs

Table of Contents

- Introduction

- FPGA and its Application

- FPGA Architecture

- Combinational Circuit and Lookup Table

- Implementing Circuits on Lookup Table

- Operational Modes of Lookup Table

- Transistor Level Implementation

- Variety of Lookup Table Sizes

- Mapping Circuits onto Lookup Tables

- Conclusion

Introduction 🌟

FPGAs (Field Programmable Gate Arrays) are fascinating implementation platforms that offer immense flexibility to implement various digital circuits. From simple adders to complex microprocessors, FPGAs provide a powerful resource for prototyping and actual system implementation. In this article, we will dive deep into the world of FPGAs, exploring their architecture and the fundamental component known as the Lookup Table (LUT). We will discuss the various operational modes of LUTs, their transistor-level implementation, and the mapping of circuits onto LUTs. By the end, you will have a comprehensive understanding of how FPGAs and LUTs work together to bring digital circuits to life. Let's get started!

FPGA and its Application 🚀

FPGAs have evolved from being mere prototyping devices to powerful implementations of entire systems. Initially used by semiconductor companies for prototyping their designs, FPGAs now find extensive application in a wide range of industries. Companies like Intel use FPGAs to extensively test their processor designs before moving to an Application-Specific Integrated Circuit (ASIC) implementation. However, with advancements in FPGA technology, these devices have become powerful enough to be directly implemented in applications, eliminating the need for a separate ASIC implementation. This shift has made FPGAs a popular choice for implementing a diverse range of systems.

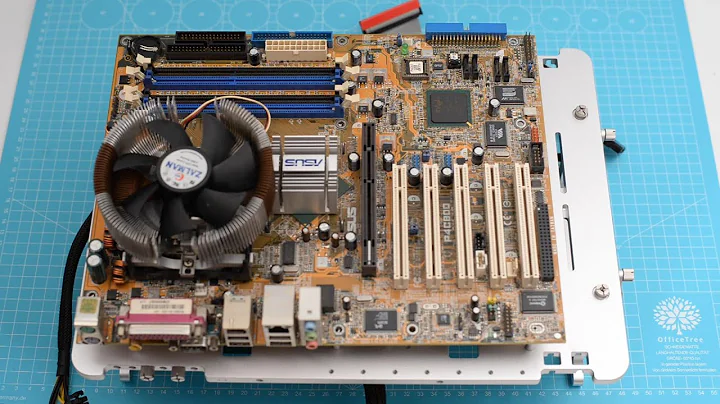

FPGA Architecture 🔩

Before delving into the intricate details, it is essential to understand the basic architecture of an FPGA. FPGAs consist of an array of configurable logic blocks (CLBs) interconnected by a programmable routing Fabric. Each CLB comprises essential components, including Lookup Tables (LUTs), multiplexers, and flip-flops. LUTs play a crucial role in implementing combinational logic circuits within an FPGA. They serve as the building blocks that can be programmed to implement any desired Boolean function. By understanding the architecture of FPGAs, we can proceed to explore the vital components that enable their functionality.

Combinational Circuit and Lookup Table 💡

Combinational circuits form the foundation of digital logic design, and Lookup Tables (LUTs) play a vital role in implementing these circuits within an FPGA. A LUT is a small memory device capable of implementing any combinational logic circuit. It consists of sets of Static Random Access Memory (SRAM) cells, which store the truth table values for a particular function. The number of inputs and outputs of a LUT depends on its capacity, with larger LUTs accommodating more complex functions. By leveraging the power of LUTs, designers can efficiently implement any desired combinational logic using a flexible and reconfigurable FPGA platform.

Implementing Circuits on Lookup Table 🔌

To implement a circuit on a LUT, it is essential to understand the configuration process and the operational modes of the LUT. There are three primary modes of operation: Combinational Mode, Load RAM Mode, and Lookup Table RAM Mode. In Combinational Mode, the LUT behaves as a standard combinational logic circuit, where the outputs are a function of the inputs. In Load RAM Mode, the LUT can be initialized with pre-defined values, allowing for runtime modification of the LUT contents. Lookup Table RAM Mode enables the LUT to function as a small sequential memory that can be written to during runtime. These modes provide designers with a flexible framework to implement a wide range of circuits using LUTs.

Operational Modes of Lookup Table 🔄

The operational modes of Lookup Tables (LUTs) provide various functionalities, enabling designers to optimize their circuit implementations. In Combinational Mode, LUTs function as simple logic gates, implementing any desired Boolean function. Load RAM Mode empowers designers to modify the contents of LUTs during runtime, facilitating dynamic circuit configurations. Lookup Table RAM Mode allows LUTs to function as small sequential memories, making them suitable for applications requiring temporary data storage. By considering the operational modes of LUTs, designers can leverage their versatility to create efficient and adaptable circuit implementations in FPGAs.

Transistor Level Implementation 💡

At the transistor level, Lookup Tables (LUTs) comprise a combination of SRAM cells and multiplexers (MUXes). SRAM cells store the truth table values of a function, while MUXes provide the required functionality to route inputs to the appropriate memory cells. This transistor-level implementation allows LUTs to be highly configurable and capable of implementing a wide range of logic functions. By understanding the underlying transistor-level circuitry, designers gain insights into the intricate workings of LUTs within FPGAs.

Variety of Lookup Table Sizes 🔢

The size of a Lookup Table (LUT) determines the number of inputs it can accommodate and the complexity of functions it can implement. Most commercial FPGAs, like Xilinx, offer LUTs in various sizes, typically ranging from 4-input to 7-input LUTs. The choice of LUT size depends on the requirements of the circuit being implemented. While smaller LUTs are suitable for most applications, larger LUTs offer the flexibility to implement more complex functions. FPGA designers must carefully analyze their circuit requirements to determine the optimal LUT size for their specific application.

Mapping Circuits onto Lookup Tables 🧩

The process of mapping circuits onto Lookup Tables (LUTs) involves dividing a circuit into smaller pieces that can fit within the capacity of available LUTs. Each piece should have fewer inputs than the maximum supported by the LUT. By appropriately partitioning the circuit, FPGA designers can map the circuit onto LUTs and effectively utilize the resources available. Modern FPGA design tools provide automatic mapping functionality, simplifying the process for designers. However, researchers and advanced users have the flexibility to develop custom mapping algorithms to fine-tune their circuit implementations.

Conclusion 📝

Lookup Tables (LUTs) serve as the fundamental building blocks of FPGAs, enabling the implementation of complex combinational logic circuits within a reconfigurable platform. By understanding the architecture, operational modes, and transistor-level implementation of LUTs, designers gain valuable insights into the inner workings of FPGAs. The flexibility and configurability offered by LUTs make FPGAs powerful tools for implementing a wide range of digital circuits. By effectively mapping circuits onto LUTs, designers can optimize FPGA resources and create efficient and high-performance designs tailored to their specific requirements. The ongoing advancements in FPGA technology promise even greater potential for implementation and innovation in the world of digital logic design.

FAQs

Q: Can I modify the contents of a Lookup Table (LUT) during runtime?

A: Yes, in Load RAM Mode, LUT contents can be modified in runtime, allowing for dynamic circuit reconfiguration.

Q: How do smaller Lookup Tables (LUTs) benefit FPGA circuit implementations?

A: Smaller LUTs offer more flexibility and efficient resource utilization, as they can implement a wide range of Boolean functions and require fewer resources compared to larger LUTs.

Q: Can Lookup Tables (LUTs) be used for sequential logic implementation?

A: Yes, LUTs can be used to implement sequential logic by leveraging the Lookup Table RAM Mode, which allows them to function as small sequential memories.

Q: What factors should be considered when choosing the size of a Lookup Table (LUT)?

A: The complexity of the circuit being implemented and the number of inputs required should be considered when choosing the size of a LUT. Smaller LUTs are generally sufficient for most applications, while larger LUTs offer more flexibility for complex functions.

Q: How are circuits mapped onto Lookup Tables (LUTs) in FPGAs?

A: Circuits are partitioned into smaller pieces, ensuring that each piece fits within the capacity of the available LUTs. The mapping process involves assigning each portion of the circuit to an appropriate LUT, optimizing resource utilization and circuit performance.

Resources:

41.4K

41.4K

54.44%

54.44%

53

53

< 5K

< 5K

13

13

14M

14M

54.77%

54.77%

16

16

< 5K

< 5K

13

13

< 5K

< 5K

0

0

< 5K

< 5K

4

4

< 5K

< 5K

1

1

< 5K

< 5K

2

2

WHY YOU SHOULD CHOOSE TOOLIFY

WHY YOU SHOULD CHOOSE TOOLIFY